1.NMOS+PMOS-構(gòu)成CMOS

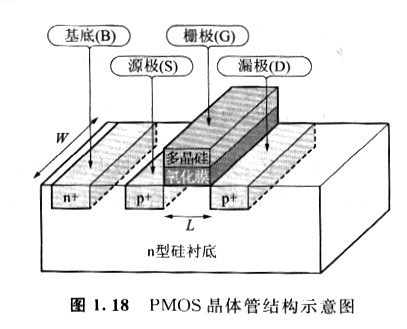

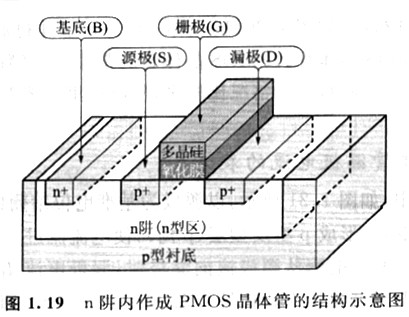

圖1. 18所示的PMOS晶體管是在n型基底上構(gòu)成p+型的源區(qū)和漏區(qū)。假如采用p型硅襯底,如圖1.19所示,在p型襯底上先作成n型基底,把這個n型區(qū)域稱為n阱( well)。

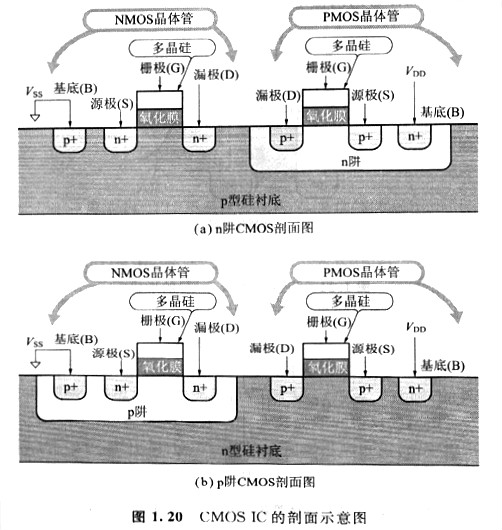

圖1. 20(a)是在p型硅襯底上構(gòu)成的CMOS剖面表示圖。以n阱為基底作成PMOS晶體管,以p型硅襯底為基底作成NMOS晶體管。

通常n阱中需介入n+區(qū)與正電源電壓VDD銜接,也有可能取獨立的電位。例如,p型硅襯底上構(gòu)成多個n阱時,也能夠其中某一個n阱與VDD銜接,而其他n阱與源極取等電位。但是p型硅襯底必需與負(fù)電源電壓銜接。就是說PMOS晶體管的基底可取的電位與NMOS晶體管相比,自在度要大。

假如運用n型硅襯底,如圖1. 20(b)所示,先在n型硅襯底上構(gòu)成p阱,作成以p阱為基底的NMOS晶體管。PMOS晶體管的基底是n型硅襯底。

普通來說,運用p型硅襯底的狀況比擬多,所以這里主要對運用p型硅襯底的狀況停止討論。

2. PMOS晶體管漏極電流的表達(dá)式

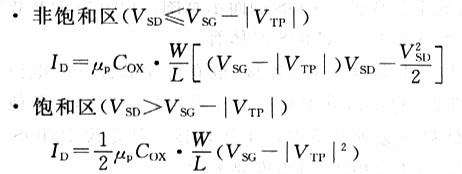

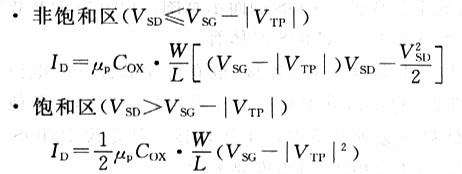

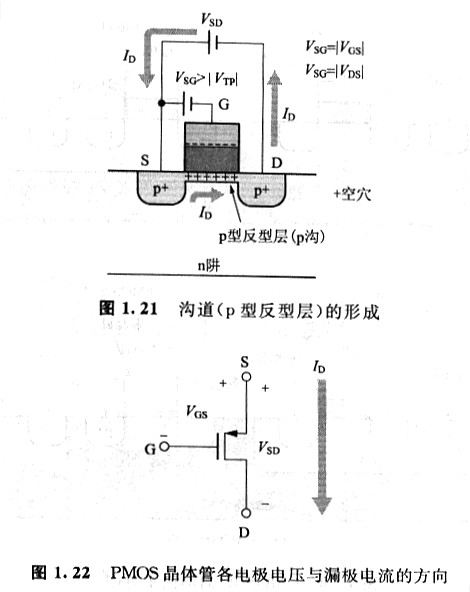

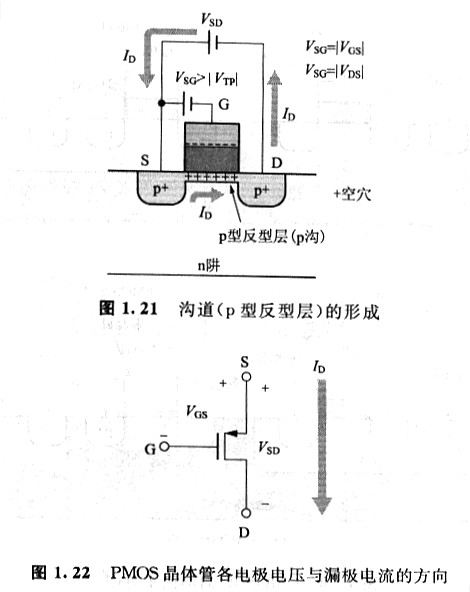

PMOS晶體管中,如圖1.21所示,以源極為基準(zhǔn)電位給柵極加負(fù)的電壓,在柵氧化膜下方感應(yīng)出空穴,構(gòu)成p型反型層(p溝),使電流流過。所以PMOS晶體管的閾值電壓VTP是負(fù)值。電流從源極流向漏極時,漏極電流ID取正值,源極—柵極間電壓V SG和源極—漏極間電壓VSD取圖1,22所示的極性時,PMOS晶體管的漏極電流ID由下式給出:

式中,VTP是PMOS晶體管的閾值電壓。

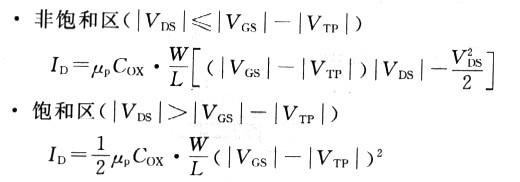

如果采用各電壓的絕對值,那么漏極電流的式(1.1)和式(1.4)也分別適用NMOS晶體管和PMOS晶體管;

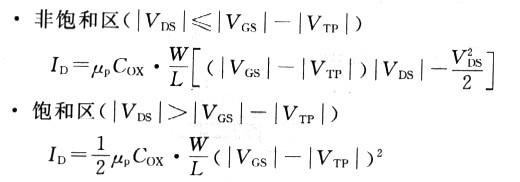

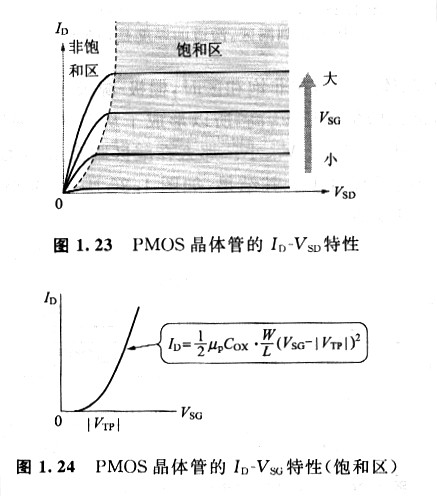

圖1. 23和圖1.24分別示出漏極電流與源極漏極間電壓的關(guān)系曲線,以及漏極電流與源極—柵極間電壓的關(guān)系曲線。

烜芯微專業(yè)制造二極管,三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹