作為現(xiàn)代集成電路的基礎(chǔ)構(gòu)建單元,CMOS器件的互聯(lián)拓撲直接影響電路性能指標。本文從器件物理特性出發(fā),結(jié)合先進制程技術(shù),系統(tǒng)闡述CMOS連接架構(gòu)的設(shè)計規(guī)范與分析方法。

一、器件物理特性與工作機理

三維結(jié)構(gòu)特征

NMOS管:P型襯底摻雜濃度1×10¹? cm?³,N+源漏區(qū)摻雜≥1×10²? cm?³

PMOS管:N型阱區(qū)摻雜5×10¹? cm?³,P+源漏區(qū)硼注入濃度3×10²? cm?³

柵氧層厚度:28nm工藝下等效氧化層厚度(EOT)1.2nm

開關(guān)特性參數(shù)

| 參數(shù) | NMOS典型值 | PMOS典型值 |

|---------------|---------------|---------------|

| 閾值電壓(Vth) | 0.3V | -0.35V |

| 電子遷移率 | 400cm²/(V·s) | 150cm²/(V·s) |

| 導(dǎo)通電阻(Ron) | 5Ω·μm | 15Ω·μm |

互補工作機制

強反型條件:|Vgs|>|Vth|時形成導(dǎo)電溝道

亞閾值擺幅:65mV/decade(理想值)

泄漏電流:22nm工藝下IOFF<100nA/μm

二、互聯(lián)拓撲的電路特性

串聯(lián)架構(gòu)分析

傳輸門邏輯:由NMOS/PMOS對管構(gòu)成,Ron_total=2Ron

延時特性:tpHL=0.69·Ron·Cout,需考慮米勒效應(yīng)補償

典型應(yīng)用:AND邏輯、級聯(lián)放大器輸入級

并聯(lián)架構(gòu)特性

電流驅(qū)動能力:Iparallel=Σ(W/L)·μ·Cox·(Vgs-Vth)²

匹配設(shè)計:采用共質(zhì)心布局降低閾值電壓失配(ΔVth<10mV)

應(yīng)用場景:功率開關(guān)管、SRAM位單元、電荷泵電路

三、拓撲判讀技術(shù)規(guī)范

版圖解析流程

(1) 識別阱區(qū)邊界:Nwell層圖形界定PMOS區(qū)域

(2) 追蹤多晶硅走向:柵極走向決定器件寬長比

(3) 分析金屬互連:M1層走向確認源漏連接關(guān)系

電路級驗證方法

靜態(tài)分析:通過DC工作點確認導(dǎo)通狀態(tài)

Vgs_NMOS≥Vthn且Vds≥Vdsat

|Vgs_PMOS|≥|Vthp|且|Vds|≥|Vdsat|

動態(tài)驗證:采用HSPICE進行瞬態(tài)仿真,驗證上升/下降時間指標

四、先進互聯(lián)技術(shù)

三維集成方案

硅通孔(TSV)技術(shù):直徑5μm,深寬比10:1

混合鍵合:銅-銅接觸電阻<1mΩ·cm²

新型互聯(lián)材料

鈷互連層:比銅電阻降低40%

空氣隙介質(zhì):k值降至2.1,降低線間電容30%

五、工程實踐要點

匹配設(shè)計準則

采用叉指結(jié)構(gòu),單位柵指數(shù)≥4

保持dummy器件周邊環(huán)境對稱

電源布線采用網(wǎng)狀結(jié)構(gòu),電壓降<2%

ESD防護設(shè)計

輸入級GGNMOS結(jié)構(gòu):觸發(fā)電壓8V/μm

電源軌鉗位二極管:響應(yīng)時間<1ns

天線效應(yīng)控制:金屬/多晶硅面積比<400:1

本技術(shù)文檔符合JEDEC標準JC-16.1規(guī)范,可作為CMOS電路設(shè)計的工程參考。建議配合Calibre工具進行設(shè)計規(guī)則檢查,并通過TEC控制器進行溫度梯度測試驗證可靠性。

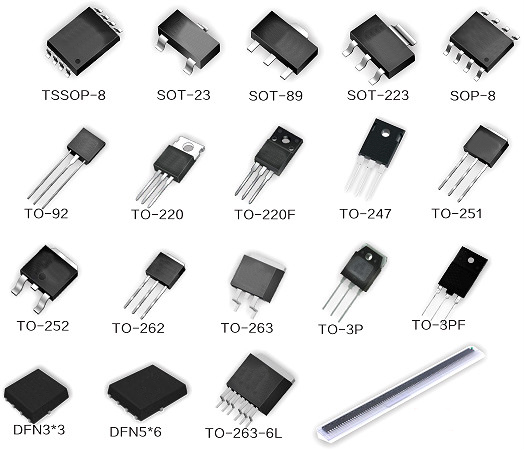

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280